The Veryl team has published a new release of Veryl, 0.16.2. Veryl is a new hardware description language as an alternate to SystemVerilog.

If you have a previous version of Veryl installed via verylup, you can get the latest version with:

$ verylup update

If you don't have it already, you can get verylup from release page.

New Language Features

Support reference to type defiend in existing package via proto package #1691

Proto typedefs are allowed to have their actual types. This allows a type symbol defined in a different package to be imported into the proto package and referenced from other components through it.

package FooPkg {

struct Foo {

foo: logic,

}

}

proto package BarProtoPkg {

type Foo = FooPkg::Foo;

}

package BarPkg for BarProtoPkg {

type Foo = FooPkg::Foo;

}

module ModuleA::<PKG: BarProtoPkg> {

var _foo : PKG::Foo;

assign _foo.foo = 0;

}

module ModuleB {

inst u: ModuleA::<BarPkg>;

}

Add const declarations to StatementBlockItems #1695

const declaration can be used in statement blocks.

function foo () -> u32 {

const bar: u32 = 2;

return bar;

}

Support embed declaration in component declaration #1712

embed declaration with sv block can be used in component declaration like module, interface and package.

module ModuleA {

embed (inline) sv{{{

initial begin

$display("hello");

end

}}}

}

New Tool Features

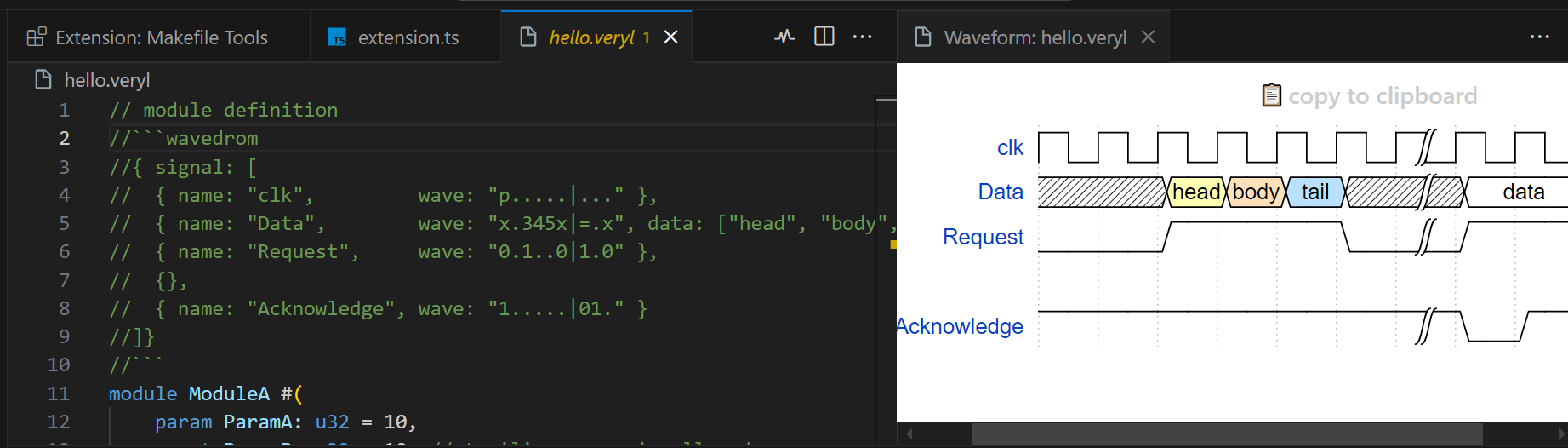

Merge Waveform Render into Veryl VS Code Extension #1713

VSCode Extension supports preview of waveform in documentation comments.

Add support for including additional files for tests #1718 #1729

Additional files for test can be specified by include_files. For example, it can be used to specify HEX files which are read by $readmemh.

[test]

include_files = ["test.hex"]

Allow to specify multiple source directories #1747

Multiple source directories can be specified via sources instead of source.

source becomes deprecated, and will be removed after a few versions.

[build]

sources = ["rtl", "tb"]

Other Changes

Check out everything that changed in Release v0.16.2.